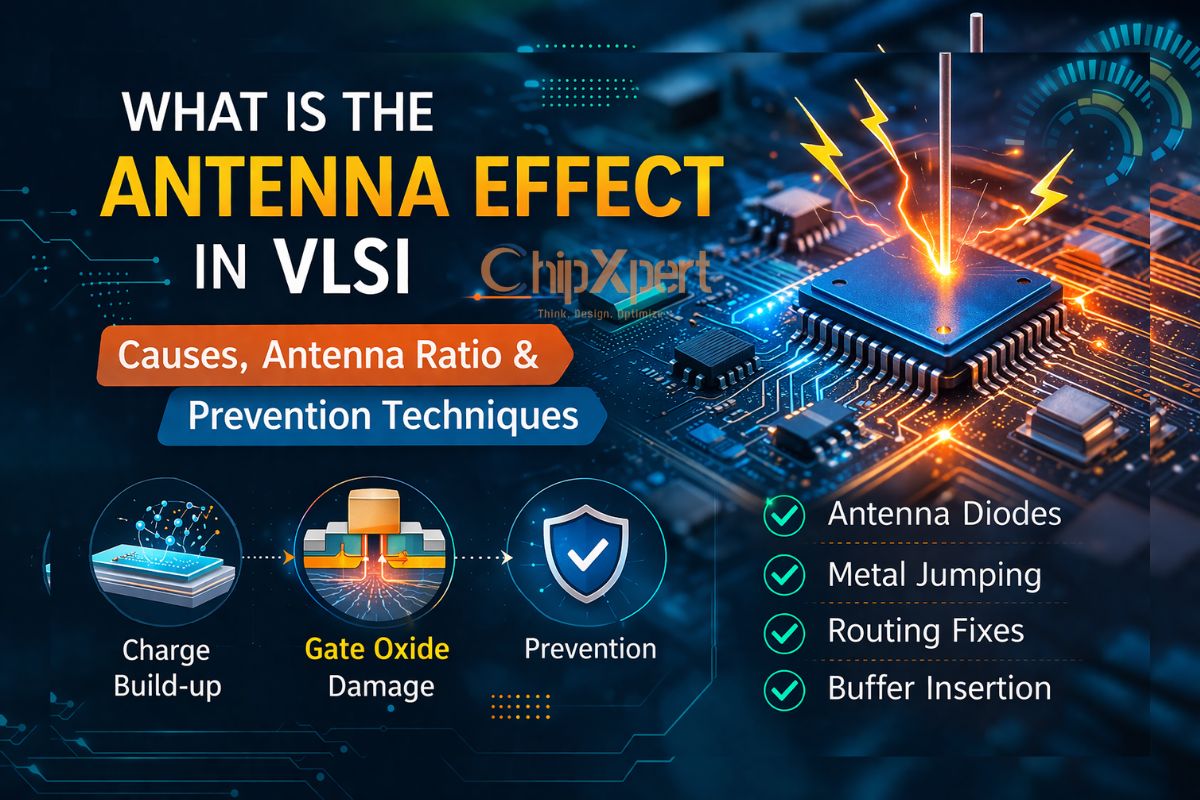

In modern semiconductor design, reliability is just as important as performance. One of the lesser-known but critical challenges in physical design is the antenna effect. Although the term may sound related to radio communication, in VLSI it refers to a phenomenon that can damage transistors during chip fabrication.

Understanding the antenna effect is essential for physical design engineers because it directly impacts manufacturing yield and chip reliability. In this article, we explore what the antenna effect is, why it occurs, and the techniques engineers use to prevent antenna violations in modern integrated circuits.

Understanding the Antenna Effect

The antenna effect occurs when long metal interconnects accumulate electrical charge during the semiconductor fabrication process. During manufacturing steps such as plasma etching, ionized particles in the plasma environment can induce charge on exposed metal structures.

If a long metal wire is connected to the gate of a transistor and there is no discharge path available, the accumulated charge can discharge through the thin gate oxide layer. This may lead to gate oxide damage or transistor failure, which reduces chip reliability and manufacturing yield.

Because the metal structure behaves like an antenna collecting charge from the plasma environment, this phenomenon is known as the antenna effect.

Why the Antenna Effect Happens During Fabrication

Unlike many other design challenges, the antenna effect primarily occurs during the manufacturing stage rather than during normal circuit operation.

Several fabrication processes can contribute to this issue:

Plasma Etching

Plasma etching is widely used in semiconductor manufacturing to remove unwanted material layers. Charged particles generated in the plasma can deposit charge on metal structures during the etching process.

If the metal is connected to a transistor gate before diffusion or power connections are established, the accumulated charge may pass through the gate oxide and damage it.

Long Metal Interconnects

Large metal areas connected to small gate terminals can collect significant amounts of charge. When the metal area becomes too large compared to the gate area, the voltage across the oxide increases, raising the risk of breakdown.

Floating Metal Segments

Metal wires that are not yet connected to power or ground during certain fabrication stages can behave like floating antennas, collecting charges from the plasma environment.

Impact of Antenna Violations

If antenna violations are not addressed during design, several problems can occur:

- Gate oxide degradation

- Reduced device reliability

- Permanent transistor damage

- Lower manufacturing yield

In advanced semiconductor nodes where gate oxide thickness is extremely small, even a small charge buildup can cause serious damage. Therefore, foundries define strict antenna rules that designers must follow during physical verification.

What Is an Antenna Ratio

In physical design, the antenna effect is typically evaluated using a metric known as the antenna ratio.

The antenna ratio compares the exposed metal area connected to a gate with the gate area itself. If the metal area becomes too large relative to the gate area, the risk of charge accumulation increases.

When the antenna ratio exceeds the limit defined by the manufacturing process, it results in an antenna violation that must be corrected before tape-out.

How Engineers Fix Antenna Violations

Physical design engineers apply several strategies to prevent or resolve antenna violations during layout and routing.

Antenna Diode Insertion

One of the most common solutions is inserting antenna diodes near the gate. These diodes provide a safe discharge path for the accumulated charge, preventing the gate oxide from being damaged.

Metal Layer Jumping

Another widely used method is switching the routing to a higher metal layer using vias. By breaking long metal segments into smaller sections across different layers, the effective antenna ratio can be reduced.

Routing Modification

Sometimes simply changing the routing path can reduce the metal area connected to the gate and eliminate the violation.

Buffer Insertion

Inserting buffers or intermediate gates can break long nets into smaller segments, which reduces the antenna ratio and protects sensitive gates.

Antenna Rule Checking in Physical Verification

Before a chip design is finalized, physical verification tools run antenna rule checks to detect violations. These checks analyze metal segments connected to transistor gates and verify that the antenna ratio stays within allowed limits.

If violations are detected, designers must apply corrective techniques before the design is considered ready for manufacturing.

Importance of the Antenna Effect in Modern Technology Nodes

As semiconductor technology continues to scale, gate oxide layers become thinner and more sensitive to voltage stress. This makes the antenna effect even more critical in advanced nodes such as 7nm, 5nm, and beyond.

Without proper antenna protection techniques, even minor charge accumulation during fabrication could lead to significant yield loss.

Conclusion

The antenna effect is a critical reliability issue in VLSI physical design that occurs during semiconductor fabrication when metal structures accumulate charge and discharge through transistor gates. If not controlled, this phenomenon can damage gate oxide layers and degrade chip reliability.

By applying techniques such as antenna diodes, metal layer switching, routing optimization, and buffer insertion, engineers can effectively prevent antenna violations and ensure reliable chip manufacturing.

For VLSI engineers, understanding the antenna effect is not just theoretical knowledge. It is a practical skill that plays a major role in delivering robust and manufacturable silicon designs.